1. LCD Interface 확인

LCD Interface 관련내용

ST LCD Interface 와 MIPI Interface 설명

- Intel8080/68K/SPI

이전에 설명했듯이 CPU/MPU Interface 와 SPI Interface이며, 주로 내부에 GRAM이 존재하여, 별도의 Fram Buffer가 필요가 없다.

- RGB Interface

1.1 LCD Interface 와 MIPI Interface의 이해

ST기반의 LCD와 MIPI Interface를 이해해보자.

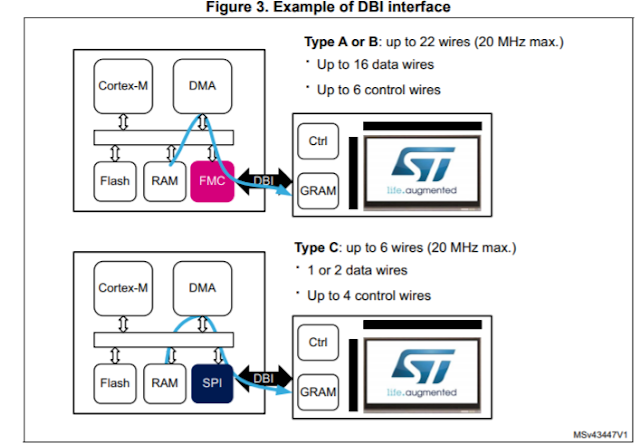

- DBI (Display Bus Interface): CPU/MPU Interface 와 SPI Interface without Frame Buffer

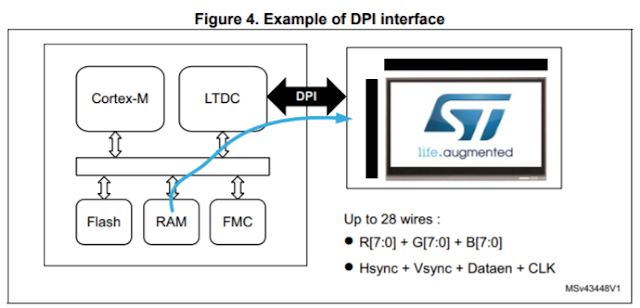

- DPI(Display Pixel Interface): RGB Interface with Frame Buffer

- DCS(Display Command Set): MIPI-DBI Interface 지원하는 Command들

- DBI 구조 (CPU/SPI Interface로 Frame Buffer가 필요 없는 Type)

- DPI 구조 (RGB Interface로 내부에 Frame Buffer가 존재)

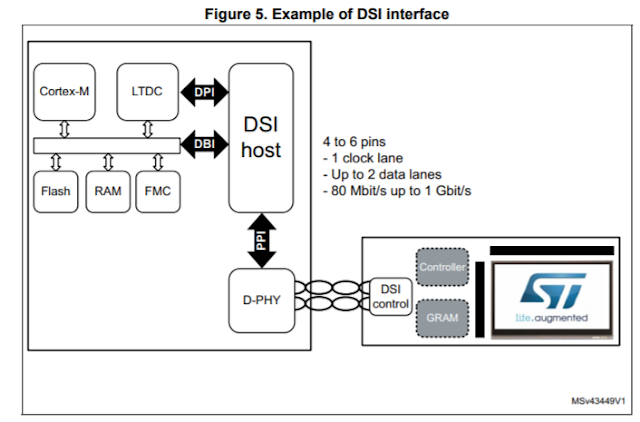

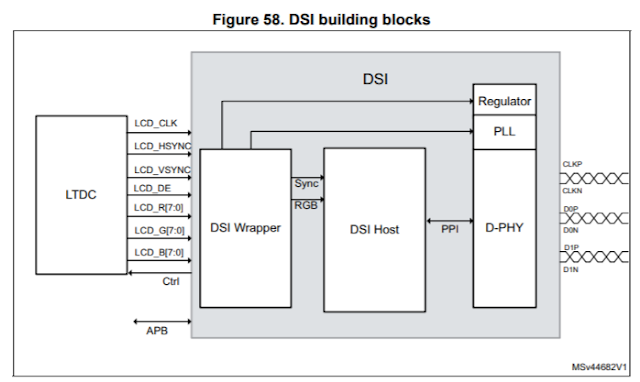

- MIPI-DSI Host 구조

DPI 와 DBI 기반으로 MIPI DSI Host(Display Serial Interface) 구축하고, PPI(PHY Protocol Interface)를 이용하여 D-PHY와 통신하여,

이를 MIPI LCD에게 전달해준다.

MIPI-DSI 를 보면 이전의 LCD Interface로 연결이 되어 이를 Host로 생성한 후 이를 MIPI-DSI로 연결하는 방식이다.

어떻게 보면 예전의 LVDS와 다르지 않게 느껴진다.

2. MIPI-DSI Host 기본구조

MIPI(Mobile Industry Processor Interface)의 DSI는 LCD Interface를 고속 Serial Interface를 이번기회에 정리하고자 한다.

MIPI(Mobile Industry Processor Interface)

MIPI-DSI(Display Serial Interface)

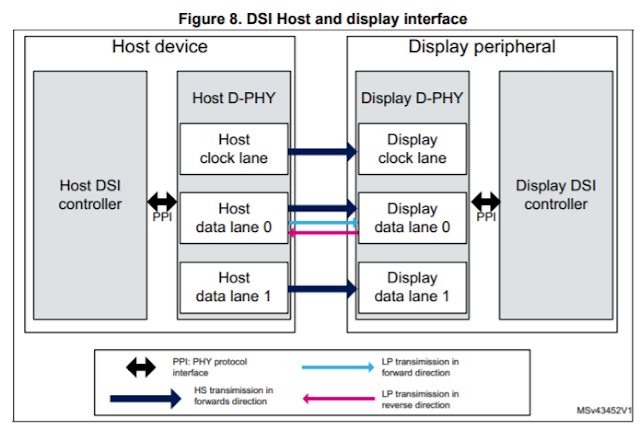

- MIPI DSI Host 와 LCD Dispaly 구조

Lane은 0~3도 가능하며, PHY는 중 1개의 Lane은 양방향통신을 진행한다.

- HS(High Speed) Mode

- LP(Low Power) Mode

상위 D-PHY기반의 PHY Protocol Interface (PPI) 말하며, 용어만 알아두도록하자.

상위 Lane들을 구조를 좀 자세히 보면 3개 중 2개 HS Mode(단방향)만 사용하며, 나머지 1개만 HS Mode 와 LP 모드(양방향)형식으로 데이타 전송이 이루어 지고 있음을 알수 있다.

즉 Host에서 상위 DCS(Display Command Set)을 LP 모드로 전송하고 DATA는 HS Mode로 전송함을 짐작할 수 있다.

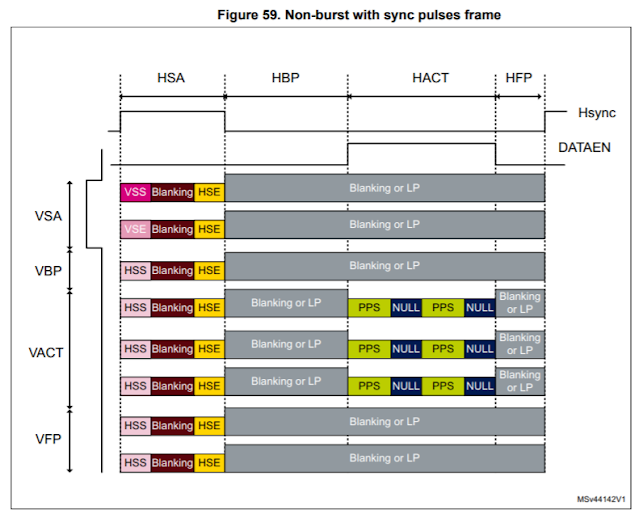

- DPI 기반의 MIPI-DSI Host 구조

아래의 경우는 상위 설명의 DPI(RGB Interface) 기반으로 동작되는 것을 MIPI-DSI Host로 연결한 구조이다.

기존의 RGB Interface와 거의 유사하며, 다만 실제 영상데이타는 PPS(HS)로 전송되며 나머지는 LP로 되어지는 것으로 보인다.

- HSA (Hsync active)

- HBP (horizontal back porch)

- HFP (horizontal front porch)

- VSA (Vsync active)

- VBP (Vertical back porch)

- VFP (Vertical front porch)

- VSS (Vsync Start)

- VSE (Vsync end)

- HSS (Hsync Start)

- HSE (Hsync end)

- PPS (Packed Pixel Stream)으로 16/24/32 등 RGB/YUV를 비롯하여 다양하다

Tegra의 DRM 의 RGB Interface 설정

상위그림은 현재 D-PHY를 사용하고 있으며, PHY 내부의 Protocol을 조금 더 알아보자.

- PHY 의 모드와 속도

- DSI PHY Signal Mode에서는 두가지 모드로 통신 구성

- HS (High Speed) Mode: 빠른 모드로 최대 1.5Gb/s 라고 하며, 상위 글을 보면 각 PHY마다 다른것으로 파악 (200mV)

- LP (Low Power) Mode: 저전력모드로 아래 그림과 같이 differtial 이 아니며, Level과 속도도 10Mb/s 밖에 되지 않는다. (1.2V)

- Data lane의 Operating Mode/ State Code

- Control Mode: Reset 후 LP-11인 상태이며, 다른모드가 종료후 이모드임

- HS Mode: 뒤에 설명

- Escape Mode: 뒤에 설명

2.2 Data lane 의 HS Mode

Control Mode 진입 후 HS Mode로 진입하여 데이타 통신을 진행하므로 반드시 알아야함

- 일반적인 HS Mode 동작

- SoT (Start of Transmission)

LP-11 (Stop), LP-01 (HS-Rqst), LP-00( Bridge) 받는 즉시 HS Mode로 진입하고 DSI Host는 HS-0과 함께 시작하며, 상위 Sync Sequence를 보낸다.

- EoT(End of Transmission)

HS모드로 Data 전송후 Host는 Trailing sequence를 보내는데, 마지막 data의 반대 값 HS-0/1

LP-11모드로 진입

2개의 Lane사용시의 Data 전송되는 방식이며, 4개도 동일하다.

2.3 Data lane의 Escape Mode

Escape Mode는 접해보지 못한것으로 아래의 Command들도 제공을 해주며, 이 부분 추후에 더 보강을 하자.

Escape Mode Command

3. PHY의 세부 동작

- 상위 Data Lane 중 양방향 통신방식을 보면 아래와 같이 동작

- Clock-lane의 Power Mode

- LP(Low Power) Mode

- HS(High Speed) Mode

- ULPS(Ultra-low-power state)

3. MIPI Spec

DSI-DCS (Display Command Set)

CSI-CCS(Camera Command Set)

CCI